【旧BBSから移行】nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2013/03/24(Sun) 00:56 |

| 投稿者 |

: Kas |

マイコンからのスイッチングでFETを使おうと思っているのですが,PチャネルとNチャネルのFETはどういう場面で使い分けるのでしょうか.

スイッチングはNでもPでも可能だということはわかりましたが,色々調べてもそれぞれをどう使い分けるのか分かりませんでした.

下記のように考えたのですが,実際にはどのように捉えるべきでしょうか.

1.【N有利】Nチャネルの方が入手しやすい

どちらでも実現可能ならば,あえてPチャネルは使わず豊富で入手のしやすいNチャネルを使う.

2.【P有利】GNDを共通にしたいからPチャネルを使う?

下記URLにもあるように,GNDが共通でなければ違和感を感じます.

ttp://todotani.cocolog-nifty.com/blog/2010/01/mos-fet-b7c9.html

しかし,

電流を遮断しいるのでスイッチングとして問題は無いと思いますし,

あえてGNDを共通にする必要はなければ,

Nチャネルを使えばいい気もします.

3.【N有利?】電源電圧が違うとき

ttp://www.marutsu.co.jp/user/fet_3.php の図8にあるような回路の場合,トランジスタが必要になると思います.

ゲートに流す電流を稼ぐという点でトランジスタを使うのもあるとは思いますが,

ソース(ソーラーの電圧)>ゲート(マイコンの5V or 0V)

が常時4V以上になって,スイッチングの役目を果たさなってしまうので

トランジスタを入れるということでしょうか.

高速スイッチングのためにゲートに流す電流を稼ぐのにTrを使うならわかるのですが,

NチャネルFETを使い0Vor5Vをゲートにかけてスイッチングすれば

トランジスタ不要になりそうなのに何故あえてPチャネルなのでしょうか.

4.仕様を満たせば何でも良い?

上記のように幾つか考慮しなければならない点もありますが,

Vthやオン抵抗などが適切な素子であれば回路は動くと思います.

結局のところ,それを選べば良いだけの話なのでしょうか.

汎用性はNの方が高い気がします.

逆に言えば,あえてPチャネルでスイッチングする利点は2のGNDを共通にできることぐらいです.

そういう理由もあって1が成り立っている?

たとえ実際は4のようなことだとしても,

個人的には「コッチを使うのが一般的」というのがあるのではないかと思うのです.

そういったFETの使い分けや,使い方の定石パターンのようなものがあれば教えていただきたいです.

(スイッチングについてでHブリッジのように両極が必要になる特殊ケースを除きます)

編集

【旧BBSから移行】ロードスイッチ設計のツボ(1)

| 投稿日 |

: 2013/03/25(Mon) 11:59 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ようこそ、いらっしゃいませ!!

ここを開設して丸一年、やっと、はじめてのお客様です。

感謝感動で胸が熱いです。ありがとうございます!

お礼の分も気合いを入れてお答えしちゃいます!!

さて、ご質問のような電源を制御する回路は最近、

「ロードスイッチ」と呼ばれ、よく見掛けるようになりました。

省エネでエコだとか、電池長持ちとか、そんな背景でしょうね。

考え方に必要と思われます、順序に沿ってご説明します。

少々長くなりますので、複数回に分けさせていただきます。

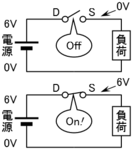

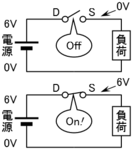

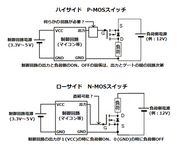

直流回路ですので、当然ながら電源から「+」と「-」の2本の

線が負荷に接続されます。この回路のオン・オフを制御するには、

「+」側か「-」側、どちらかにスイッチを挿入する事になります。

(両方に挿入するのは、中高圧以上の別世界の話です)

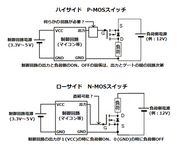

「+」側に挿入する場合、「ハイサイドスイッチ」と呼ばれます。

「-」側に挿入する場合、「ローサイドスイッチ」と呼ばれます。

あるいは省略して、「ハイサイド」「ローサイド」と呼んだりも

します。図も併せてご確認ください。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(2)

| 投稿日 |

: 2013/03/25(Mon) 13:14 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ここから先は、設計者のスキルや嗜好によって意見が異なったり、

そもそも私自身が間違った認識のままでいたりする可能性も

ありますので、その旨ご了承ください。

異論・反論・ツッコミも大歓迎です。是非お寄せください。

結論を先に申し上げると、ハイサイドスイッチを多用します。

理由は、常時電源オンの回路(図中の回路A)と電源オン・オフが

制御される回路(図中の回路B)の間で信号伝達が行われる場合が

往々にしてあるためです。

デジタル信号にしてもアナログ信号にしても、通常の方法では

(シングルエンドと呼ばれます)GNDを共通の基準電位として

伝達が行われます。

電源の入っていない回路との間で信号伝達が行われるのか?

との疑問に対しては、いささかおかしな表現にはなりますが、

電源オフの回路出力には無信号が現れています。

また電源オフの回路入力には無信号が与えられて然るべきです。

これら無信号の正体は0Vで、GNDを基準電位にしての0V、つまり

GNDと同電位を意味しています。

たとえ電源オフの回路であっても、基準電位であるGNDを切断

されてしまっては都合が悪いわけです。

まだまだ続きます。図も作成しながらになりますので、

多少の時間が掛かってしまいます事をご容赦ください。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(3)

| 投稿日 |

: 2013/03/26(Tue) 13:45 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

編集

【旧BBSから移行】ロードスイッチ設計のツボ(4)

| 投稿日 |

: 2013/03/26(Tue) 14:17 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

これまでのまとめと、最終結論にも触れておきます。

▼ハイサイドかローサイドか?

→ハイサイド。共通基準電位GNDは切断したくない。

※アプリケーションによっては例外もあるでしょう。

▼PチャネルかNチャネルか?

→正電源ハイサイドならPチャネル。ゲート駆動が容易なため。

まとめと最終結論は以上です。

さて、上図にP/NチャネルMOSFETの回路図記号と端子名、ゲート-ソース間電圧VGS、ドレイン電流IDの向きを示しました。端子名はGDSそれぞれゲート/ドレイン/ソースの略です。

FET(電界効果トランジスタ)は、ゲート-ソース間電圧VGSによってドレイン電流IDを制御する部品です。

MOS(金属酸化物半導体)FETはそのほとんどがエンハンスメント型と呼ばれる特性を持ち、一定範囲のゲート-ソース間電圧VGSを掛けるとドレイン電流IDが流れます(ドレイン-ソース間がオンになる)。ゲート-ソース間電圧VGSを掛けない(0V)とドレイン電流IDが流れません(ドレイン-ソース間がオフになる)。

再び上図をご覧ください。ドレイン電流IDの向きが示されています。ドレイン電流IDはこの向きにしか流すことができません。

もし逆向きに流そうとすると、回路図記号にはダイオードが含まれています。このダイオードを通じて常に流れてしまい(常時オン)、スイッチとしてこれをオフする事はできません。

このダイオードは寄生ダイオードやボディダイオードと呼ばれ、MOSFETには必ず付いて回る存在のようです(例え不要であっても、です)。

ドレイン電流IDをオン/オフするには、矢印の方向にしか使用できません。言い換えると、電流の向きによってドレイン・ソースの接続がおのずと決定される事になります。

長くなって恐縮ですが、まだ続きます。

図を作成しますので、また少々のお時間をください。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(5-1)

| 投稿日 |

: 2013/03/26(Tue) 23:45 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ハイサイドスイッチ、PチャネルMOSFETを使用した場合の回路略図です。

図中の矢印はドレイン電流IDを示しています。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(5-2)

| 投稿日 |

: 2013/03/26(Tue) 23:46 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ハイサイドスイッチ、NチャネルMOSFETを使用した場合の回路略図です。

図中の矢印はドレイン電流IDを示しています。

編集

【旧BBSから移行】nMOSとpMOS-FETの使い分け,選び方についてロードスイッチ設計のツボ(5-3)

| 投稿日 |

: 2013/03/26(Tue) 19:28 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ローサイドスイッチ、PチャネルMOSFETを使用した場合の回路略図です。

図中の矢印はドレイン電流IDを示しています。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(5-4)

| 投稿日 |

: 2013/03/26(Tue) 23:48 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ローサイドスイッチ、NチャネルMOSFETを使用した場合の回路略図です。

図中の矢印はドレイン電流IDを示しています。

編集

【旧BBSから移行】nMOSとpMOS-FETの使い分け,選び方についてロードスイッチ設計のツボ(6)

| 投稿日 |

: 2013/03/27(Wed) 11:04 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

以上、4つの図に示しました通り、ハイサイドとローサイド、PチャネルとNチャネル、いずれの組み合わせも…従いまして4通り、全てが可能です。

MOSFETをオフにするにはゲート-ソース間電圧VGSを0Vにする。オンにするにはVGSを一定範囲にすれば良い事は、以前にお話しました。

ソースはすでに回路の一部に接続されていますので、ここの電位を自由に変えるわけにはいきませんので、ゲート-ソース間電圧VGSを操作するという事は、ソース電位に対して相対的にゲート電位を操作する事になります。このゲート電位の操作を、「ゲートの駆動」や「ゲートを駆動する」と表現する事が多いです。

従いまして、ソース電位がわかっている必要があります。そうでなければ、ゲート電位をどうすれば良いかわかりません。

4つの図それぞれのソース電位を調べてみましょう。図中のMOSFETはスイッチに置き換えて見てください。

▼(5-1)の図:ハイサイドスイッチ、PチャネルMOSFETを使用した場合

→ソース電位は常に一定(電源の+電位)

▼(5-2)の図:ハイサイドスイッチ、NチャネルMOSFETを使用した場合

→ソース電位は変化する

…スイッチオン時:ほぼ電源の+電位

…スイッチオフ時:恐らく/概ね電源の-電位

▼(5-3)の図:ローサイドスイッチ、PチャネルMOSFETを使用した場合

→ソース電位は変化する

…スイッチオン時:ほぼ電源の-電位

…スイッチオフ時:恐らく/概ね電源の+電位

▼(5-4)の図:ローサイドスイッチ、NチャネルMOSFETを使用した場合

→ソース電位は常に一定(電源の-電位)

ソース電位が一定でいてくれるのなら、ゲート電位も単純に設定できます。この実現はもちろん単純で簡便になります。

ソース電位が変化すると、ゲート電位もそれに追随して変化しなければ、所望のゲート-ソース間電圧VGSとはなりません。この実現はやや複雑で面倒になります。

以上から、既に触れました最終結論となります。

・ハイサイドスイッチにはPチャネルMOSFET

・ローサイドスイッチにはNチャネルMOSFET

ただし、これは制御回路(オン/オフを決定し、それに従ってMOSFETのゲートを駆動する回路)と負荷が同一電源・GNDで動作するよう構成されている場合に限ります。(2)の図ですと、制御回路が回路A、負荷が回路Bにあたります。

この後の記事では、この前提でのまとめと具体的な回路設計の留意点等について解説したいと思います。さらにその後の記事で、この前提があてはまらない場合について展開していく予定です。図もちゃんと起こします。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2013/03/28(Thu) 00:04 |

| 投稿者 |

: Kas |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

丁寧な解説ありがとうございます.

どういう事情,設計思想で使い分けるのか,モヤモヤしていた部分が分かって来ました.

続きの解説を楽しみにしています.

ここで,2つほど疑問が浮上したので,後ほど加えて解説頂けると嬉しいです.

回路を扱う中では,GNDを共通にしたいという場面が多いはずです.

先の最終結論から,つまりハイサイド=Pチャネルの方が扱いやすいという事になると思います.

にも関わらず販売種類としてはPチャネルが少ない気がします.

【1】NMOSのキャリアである電子が,ホールよりも優れている(移動度など)から高性能にしやすい(=種類豊富)

という認識でよろしいのでしょうか.

それとも,単に,需要の問題なのか

【2】ローサイドスイッチの需要

NMOSが多い→ローサイドスイッチも多くの場面で使われる?(個人的にはPの方が使いやすい気がするので)

具体的にどのような場面でローサイドスイッチが利用されているのか気になります.

よろしくお願いします.

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2013/03/28(Thu) 14:23 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

追加のご質問もありがたいです。

「そこは違う」なんて、ツッコミや横ヤリが入ると盛り上がるし、何より複数の方の間で知識・認識・経験の共通項が見出せれば、情報の精度・確度・信頼度も格段に上がるのでいいなとは思っているのですが…、ここの認知度ってまだまだ低いのですよね…。何とかならないかな…。

愚痴はさておき、

ご質問【1】について私が認識出来ているのは、NチャネルMOSFETと比較してPチャネルMOSFETは、

・圧倒的に品種が少ない

・同価格帯では性能が見劣りする…同性能帯では価格が高い

の2点です。ただし、ここ10年程でこれらの状況はかなり改善されてきているように見えます。

背景については私の知識が及ばないのですが、調べてみましたところ、挙げていただきました2点とも理由になっているようです。インターネットWWWからの情報なので、信憑性はいまひとつですが。

http://okwave.jp/qa/q7087822.html

http://oshiete.goo.ne.jp/qa/4433479.html

ご質問【2】につきましては、ローサイドのロードスイッチとしての用途よりも、ハーフ/フルブリッジの下アームとしての用途が圧倒的に多いはずです。上アームにもNチャネルMOSFETが使用されるケースも多いようです。

これ(上アームにNチャネル)ってソース電位が変化するのでゲート駆動が困難である点は以前にお話したのですが、継続的にオンまたはオフするロードスイッチとは異なり、ハーフ/フルブリッジは周期的にオン/オフを繰り返すものです。

オン時間が限られているのなら、コンデンサへの蓄積を利用して一時的に浮いた…元の基準電位から切り離して、任意の点を基準電位にしてしまう…電位を作ってしまおうというアプローチで考案された回路が利用されています。チャージポンプやブートストラップと呼ばれるものがそれです。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(7-1)

| 投稿日 |

: 2013/03/28(Thu) 14:37 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

編集

【旧BBSから移行】ロードスイッチ設計のツボ(7-2)

| 投稿日 |

: 2013/03/28(Thu) 14:38 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

編集

【旧BBSから移行】ロードスイッチ設計のツボ(8)

| 投稿日 |

: 2013/03/31(Sun) 15:08 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

すみません、2日も間が空いてしまいました。

上の2つの図はどちらも、以前にお話しました、制御回路と負荷が同一電源・GNDで動作するよう構成されています。(7-1)の図はハイサイドスイッチでPチャネルMOSFETを使用したもの。(7-2)の図はローサイドスイッチでNチャネルMOSFETを使用したものです。

これらのパターンに当てはまる場合、制御回路はとてもシンプルに実現出来ます。

そうそう、もうひとつ大切な条件があります。電源電圧程度のゲート-ソース間電圧VGSにおいて、実用的に低いオン抵抗が得られる事です。MOSFETのデータシートには一定のVGSにおけるオン抵抗の代表的特性や、VGS対オン抵抗のグラフの記載がありますので、そこから判断出来ます。

また、大抵の小電力用MOSFETは、ゲート入力容量Cissが1000pF程度以下に収まっています。これらの場合、制御回路はマイコンの出力ポート等のCMOSロジック出力をそのまま利用出来ます。TTLロジック出力やオープンコレクタ出力、オープンドレイン出力は適していません。

ゲート入力容量Cissが1000pFを超えていても、制御回路側がフルスイング出来ており、スイングに掛かる時間が許容範囲内であればいいでしょう。そうでなければロジック出力の先にプッシュプルエミッタフォロワを追加します。

さて、上の2つの図にあります抵抗R1,R2の説明をします。R1は制御回路の出力がフローティング状態の場合に、ゲート-ソース間電圧VGSを0Vに固定する役割があります。値は厳密ではなく、100kΩ〜1MΩの間でいいでしょう。

R2は寄生振動、回路中の寄生素子で共振現象を起こそうとするはたらきを抑える役割があります。小電力スイッチでは省略したり、中電力では保険的に100Ω程度を入れる場合が多いです。大電力スイッチでは寄生振動のリスクがいよいよ高くなるので、実験的に値を決定しているようです。

R1,R2とも、MOSFETの極力近くに配置実装するのが望ましいです。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(8・余談)

| 投稿日 |

: 2013/03/31(Sun) 15:25 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

制御回路がマイコンの出力ポートそのままの場合、マイコンの品種にもよりますが、リセット中、およびリセット解除からプログラムが動き出して、ポートの設定(入力か出力か)が行われるまで、対象のポートは入力ポートとして、つまりフローティング状態になっている場合が多いと思います。従ってあらゆるケースでR1は省略不可と考えて良いと思います。

私がMOSFETを利用しているのはここ数年の事です。それ以前はVGSに高電圧(10V以上がザラ)を要求されたり、その上オン抵抗がまだまだ大きかったりで、使う気になれませんでした。今でも国内メーカー製のMOSFETはそうだったりします。海外メーカー製MOSFETが以前より安価に入手出来るようになったのも一因です。

国内半導体メーカーの姿勢に疑問を感じているのは、MOSFETだけの事ではないんですけどね。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(8・追加図)

| 投稿日 |

: 2013/03/31(Sun) 15:58 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ゲート入力容量Cissが大きいMOSFETを使用する場合に追加するプッシュプルエミッタフォロワの回路の例です。トランジスタは一般小信号用のもので充分です。図中のベース抵抗100Ωは駆動能力(ゲート入力容量を素早く充放電する能力)を決定します。なので、値の適否は実際の充放電の様子を見て判断するのが良いでしょう。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(8・追加図-2)

| 投稿日 |

: 2013/04/01(Mon) 23:53 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ローサイドスイッチ・NチャネルMOSFETにプッシュプルエミッタフォロワを追加する場合も同じです。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(9)

| 投稿日 |

: 2013/04/02(Tue) 00:10 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

制御回路はマイコン等のデジタルロジックである事がほとんどかと思いますので、これを前提に、一旦のまとめを行います。

ハイサイドスイッチ・PチャネルMOSFETの場合、Highレベル…ほぼ+電源レベルを出力するとMOSFETはオフ状態となります。Lowレベル…ほぼGNDレベルを出力するとMOSFETはオン状態となります。

ローサイドスイッチ・NチャネルMOSFETの場合、Lowレベル…ほぼGNDレベルを出力するとMOSFETはオフ状態となります。Highレベル…ほぼ+電源レベルを出力するとMOSFETはオン状態となります。

Highレベル・Lowレベルが入れ替わって、覚えるには少々ややこしいですが、ソースがどこに接続されているか(+電源側かGND側か)を見て、そことゲートをほぼ同電位にすればMOSFETはオフ状態となります。逆側に振ればオン状態となるわけです。

なお、これらの関係は、上の図にありますプッシュプルエミッタフォロワを追加した場合も変わりません。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2013/04/03(Wed) 02:26 |

| 投稿者 |

: Kas |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

詳しくありがとうございます!

ブートストラップなど調べてみましたが,非常に面白い(画期的な)回路ですね.

nMOSが多く使われる理由も分かった気がします.

ゲート入力容量の話は興味深いです.

実際に,ゲートの電位だけ変えれば良いのかといえば,ゲートにチャージする必要があるから多分そうではないのだろうという気はしていたのですが,

やはりトランジスタを入れるのが一般的なわけですね.

データシートに書いてあるのかもしれませんが,動作検証というか素子の特性を測りたくなってきてしまいますね.

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2013/04/07(Sun) 21:46 |

| 投稿者 |

: 管理人 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ブートストラップは巧妙ですね。設計しろと言われると…無理かな?(苦笑)今では専用ICも多く出回っているので助かっています。

小電力ではさほど気にしないのですが、大電力のスイッチではオフからオンへ、オンからオフへ変化する際の過渡状態…動特性も重要になります。オフまたはオンが続く定常状態…静特性は設計時に机上で評価できてしまうのですが、動特性は実機評価が欠かせないようです(経験は無いのですが)。

バイポーラトランジスタにしてもMOSFETにしても、定格として定められている上限値は、電圧・電流・電力の3つに加え、接合部最高温度Tj(Max.)があります。

▼バイポーラトランジスタ

・コレクタ・エミッタ間最大電圧Vceo(Max.)

・コレクタ最大電流Ic(Max.)

・コレクタ最大損失電力Pc(Max.)

▼MOSFET

・ドレイン・ソース間最大電圧Vdss(Max.)

・ドレイン最大電流Id(Max.)

・ドレイン最大損失電力Pd(Max.)

これらのいずれも超えないような領域を、安全動作領域(Area of Safety Operation; ASO)と呼びます。電圧対電流グラフにプロットすると、原点を左下、最大電圧と最大電流を右上とした長方形で、右上角が最大電力を超えないよう斜めに切り落とされた領域になります。

これらは間接的に、接合部温度の上昇に対する余裕度を表していますので、周囲温度が高いと接合部温度も高く、余裕度は減少するので、安全動作領域ASOは狭くなります。

さてさて、MOSFETを使用したロードスイッチについて、まだその1パターンを紹介したに過ぎません。もうしばらくの間、不定期ながら続いていきますので、どうぞお付き合いください。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(10)

| 投稿日 |

: 2013/04/19(Fri) 18:26 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

編集

【旧BBSから移行】ロードスイッチ設計のツボ(11)

| 投稿日 |

: 2013/04/19(Fri) 18:43 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

1週間以上も間を空けたらダメですよね…。すみません。

投稿者名が「管理人」では少々お堅い感じがしますので、通常記事の投稿時には「中の人1号」と改名させていただきます。管理・運営上必要のある投稿をする場合には「管理人」を名乗らせていただきます。あらためまして、どうぞよろしくお願いいたします。

また先日、閲覧数が1000件を突破しました。ご覧いただいている方々にはただただ感謝です。ありがとうございます。

前回の記事で書きそびれましたが、それなりの(感覚的には数百mAを超えるあたりからでしょうか。高めの電圧を扱う場合や、周囲に敏感な回路があると、もっと小さな電流でも考慮が必要な場合もあり得ます)負荷電流をスイッチする場合、そのオン/オフの速度が速いと、時間当たりの電流変化率dI/dtが大きくなり、周囲にノイズを誘起したり、また負荷にインダクタンス成分を多く含む場合は無視し難い誘導起電力が発生してしまいます。スイッチング速度(オン/オフに掛かる時間)は早ければいいというものでもないという事もご留意ください。

さて、上の図は制御回路と負荷の電源が異なり、GNDは共通となる場合の回路構成例です。図中左側が負荷用の電源、その右隣が制御回路用の電源です。

結論から先に行きますと、制御回路からLowレベルを出力するとMOSFETはオフ状態となります。Highレベルを出力するとMOSFETはオン状態となります。

それぞれの場合の動作を追って行きましょう。制御回路からLowレベル…ほぼGNDレベルが出力されていると、R3を通ってバイポーラトランジスタ(以下、単にトランジスタとします)のベースからエミッタへは電流は流れません。従ってトランジスタはオフ状態となり、コレクタからエミッタへの電流も流れません。MOSFETのゲート-ソース間電圧VGSはR1によって0Vとなり、MOSFETがオフ状態となるわけです。

制御回路からHighレベル…ほぼ+電源レベルが出力されていると、R3を通ってトランジスタのベースからエミッタ、GNDに向かう電流が流れます。教科書通りだと、この電流のhfe(トランジスタの電流増幅率)倍の電流がコレクタからエミッタ、GNDに向かう電流が流れます。実際にはR1とR2によって制限され、(R1+R2)/負荷用電源電圧以上は流れない事になります。トランジスタにとってより多くのコレクタ電流を流したくても流せない状態を、飽和と呼びます。R3にはトランジスタが充分飽和する値を設定します。すごく大雑把ですが、(R1+R2)/負荷用電源電圧の1/50以上の電流がベースに流れるように設定すれば大体大丈夫です。ここに使用するトランジスタ(多くの場合、小電力用)のhfeが100程度はあるため、その場合に飽和させるベース電流の、さらに倍を流しておけば充分という根拠によるものです。

この回路構成では、MOSFETのオフ→オンはそこそこ早いのですが、オン→オフが遅いです。その際ゲート-ソース間に充電された電荷をR1だけで放電しているからですが、オン・オフの頻度が低いロードスイッチとしての応用であれば、そんなに問題にはならないかなと思います。

制御回路と負荷の電源が異なり、+側が共通という場合はあまり無い(と思います)ので省略しますが、+側もGNDも共通でない場合の方法が流用できますので、次回の記事を参考にしてください。次回まではあまり時間が空かないよう、自分に言い聞かせておきます。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(12・図1)

| 投稿日 |

: 2013/04/25(Thu) 12:01 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

編集

【旧BBSから移行】ロードスイッチ設計のツボ(12・図2)

| 投稿日 |

: 2013/04/25(Thu) 12:02 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

編集

【旧BBSから移行】ロードスイッチ設計のツボ(12)

| 投稿日 |

: 2013/04/25(Thu) 12:45 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

すみません、図をアップしただけで時間切れになってしまいました…(泣

制御回路と負荷の電源が異なり、+側も-側(GND)も接続されていない=絶縁されている場合の回路構成例です。

図中の黄色の部分は初登場の構成要素で、フォトカプラと呼ばれる部品です。

この記事に追記して、フォトカプラという部品の概要からご紹介したいと思います。

次回の更新は4/28(日)の予定です。こうご期待!

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2013/04/28(Sun) 11:44 |

| 投稿者 |

: kas |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

”

この回路構成では、MOSFETのオフ→オンはそこそこ早いのですが、オン→オフが遅いです。その際ゲート-ソース間に充電された電荷をR1だけで放電しているからですが、オン・オフの頻度が低いロードスイッチとしての応用であれば、そんなに問題にはならないかなと思います。

”

言われてみれば確かにそうですが,気づきませんでした.

奥が深いです.

フォトカプラの話題も興味があります.

モーターとマイコンの電源を分離させたくて使ったという知り合いがいるのですが,

フォトカプラの応答が遅く,結果的にFETのスイッチングが遅くなってしまった(思ったような綺麗な矩形波が出なかった)と聞いています.

(ただし当時,上の回路図にあるように直にFETのゲートに入れており,トランジスタを介す等はしていなかった気がします.)

電源を分離できるというメリットと引き換えに,応答を犠牲にするのは仕方ないことなのか,

何か上手い方法があるのか

この点についても言及して頂けると嬉しいです.

編集

【旧BBSから移行】ロードスイッチ設計のツボ(13)

| 投稿日 |

: 2013/04/28(Sun) 22:43 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

オープンコレクタ(バイポーラトランジスタの場合)やオープンドレイン(FETの場合)で構成される駆動回路が遅い原因は、回路の非対称性にあります。

記事「ロードスイッチ設計のツボ(10)」の回路例では、ロードスイッチ用MOSFETのゲート駆動回路をオープンコレクタで構成しています。

この部分を簡略化したものが、今回の図です。

MOSFETのゲートは、ほぼ100%の容量性負荷です。これを駆動するという事は、容量を充電する事、そして放電する事です。そして駆動回路には駆動能力と言われる限界があります。吐き出せる/吸い込める電流の上限で表されたり、インピーダンスで表されたりします。

駆動回路における非対称性とは、吐き出し/吸い込みの電流上限が異なるという事です。図ではスイッチ(実際の回路におけるトランジスタを簡略化して、スイッチに見立てています)がONの時に容量性負荷からスイッチを通して放電が行われ、オフのときに抵抗を通して充電が行われます。オン状態のスイッチ(にあたるトランジスタ)はインピーダンスが低く、多くの電流を流せるでしょうから、放電は短時間で完了するでしょう。抵抗はほぼインピーダンスそのもので、電流を制限しますから、充電にも相応の時間を要してしまうでしょう。抵抗値を小さくするにも限度があります。

従って遅いとは言っても、スイッチにあたるものがオフ→オンへの変化では速いです。オン→オフへの変化が遅いのですね。オープンコレクタ/オープンドレイン、あるいは3ステートのロジック出力とプルアップ抵抗の組み合わせでも同じ状況になります。

記事「ロードスイッチ設計のツボ(8)」で紹介しました駆動回路はプッシュプルエミッタフォロワ構成です。今回の図における抵抗もスイッチで構成し、交互にオン/オフするもので、充電も放電も低インピーダンスで短時間で行います。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(13・補足)

| 投稿日 |

: 2013/04/28(Sun) 23:40 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

予定ではフォトカプラの解説に入る頃合ですが、話題がホットな内に少し補足します。

先程の簡略図中の抵抗は、これまでに紹介しました回路例ではゲート-ソース間並列抵抗R1に相当します。この値を小さくすればオン→オフへの変化時間を短縮できますが、ここに流れる電流は感覚的に、せいぜい数mAまでかなと思います。緊急避難だとしても数10mAで、100mA以上だと小信号用トランジスタではIcまたはPcの定格オーバーを心配しなくてはなりません。

もう1点、スイッチング速度はロードスイッチ用途よりもチョッパ/パルス駆動用途において要注意項目となります。オン/オフの頻度の高さがその理由になります。

チョッパ/パルス駆動はPWM,PFM,PDM…、いろいろな亜種がありますが、どれも短時間でオン/オフを繰り返します。ロードスイッチのオン/オフは不定期で、その頻度も格段に低いです。

オフ→オンあるいはオン→オフが遅い、時間が掛かっているという事は、オフとオンの中間の状態に長く留まっているわけで、この状態ではスイッチング素子で損失…つまり不要な電力消費が発生します。

スイッチング損失の観点では、スイッチング速度は速いに越した事はありません。負荷回路に発生するサージや輻射/誘導ノイズを抑える観点ではスイッチング速度を程々に抑える必要があるので、これらとの兼ね合いで決定する事になります。

編集

【旧BBSから移行】ロードスイッチ設計のツボ(14)

| 投稿日 |

: 2013/05/06(Mon) 23:40 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

スイッチング速度が遅いとスイッチング損失が発生する、いや増加するが正しいでしょうか。そんなお話を前回しましたが、では実際にどれ程の損失になるのか。実は考えた事も、考えなければならない状況に遭遇した事もありませんでした。

ですので、あらためて考察を兼ねたシミュレーションを行いました。自らにとって関わりのある事象について、きちんと考察や実験あるいは調査を行い、得られた結果を図表なり文章でまとめる。こういった当たり前の事ができる事、またできるために必要な時間的余裕が得られる事は、技術者にとって、いや技術者以外の職種でもそうかな?幸せな事だと、最近思います。逆もまた真なりだとも思います。

左のグラフは、電圧一定の電源と、抵抗値一定の負荷との間に(MOSFETなどの)スイッチ素子を挿入した回路でのシミュレーション結果です。横軸はスイッチ素子の等価抵抗で、左端がとても小さな値(ほぼ0)、右端がとても大きな値(ほぼ∞)です。縦軸は負荷とスイッチ素子での電力消費で、青色が負荷、赤色がスイッチ素子です。ちなみに横軸は対数です。

スイッチ素子がオン状態の時、つまり等価抵抗がとても小さな値(ほぼ0)の時、負荷での電力消費が最大と言いますか、本来の電源供給状態となります。スイッチ素子での電力消費はほぼ0となります。

スイッチ素子がオフ状態の時、つまり等価抵抗がとても大きな値(ほぼ∞)の時、負荷での電力消費がほぼ0と言いますか、本来の電源遮断状態となります。スイッチ素子での電力消費はこちらもほぼ0となります。

スイッチ素子がオンとオフの中間の状態の時に、スイッチ素子での電力消費が発生します。赤色の線が山型に盛り上がっている部分がそれです。山の頂上が最大の電力消費を意味します。この時、青色の線と交差しています。

このグラフから、負荷の抵抗とスイッチ素子の等価抵抗が等しい時に、スイッチ素子での電力消費は最大となります。その際それぞれにおける電力消費も等しくなり、負荷本来の電力消費(青色の線の左端における高さ)の1/4となります。例えば60Wを消費する負荷にスイッチ素子を挿入して、それぞれの等価抵抗が等しくなる時に、負荷で15W、スイッチ素子で15Wの電力消費となります。

等しい抵抗値が直列に挿入されて、合成抵抗は2倍になるので電流も電力も1/2、電力は等しく分け合って消費するのでさらに1/2、なので1/4。当然と言えば当然の結果ですね。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2014/05/25(Sun) 20:25 |

| 投稿者 |

: indziine |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

はじめまして。

WEB検索からこの記事に辿り着いてある程度読み進めたのですが・・・・・・

めちゃくちゃ分かり易いです!

図が、文章が、なんて的確なのかと惚れ惚れしました。

なぜそうした方が良いのかポイントはどこなのか、自分で考えて回路を

作れるように解説されていると感じます。読みやすい文を追っていけば

1つ1つ自然に理解できてどんどん理解が深まる構成なのも秀逸です。

専門的なことをスポンジに水が染みこむように理解させられるこれは、

ちまたの解説の中でも突出しているんじゃないでしょうか。

中の人1号さんが解説書を出すなら僕は即買いします。

あまりの良解説っぷりに思わずこんな返信を書いてしまいました。

おかげさまで自分の疑問点も解決して次へ進めます。ありがとうございました。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2014/05/25(Sun) 23:46 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

indziineさんはじめまして!ようこそいらっしゃいませ!!

思いも掛けないお褒めのお言葉をいただいて、照れております…(〃▽〃

真理になかなかたどり着けずに、遠回りした者ほど、

そこに至るまでの道程に何があったかを覚えていて、

似た境遇に戸惑う方々をご案内して差し上げたりできるものです。

実務の現場では数多くのHowが要求されますが、これらの根幹にある

Whyの理解が無ければ、その場しのぎになってしまい、苦労が絶えません。

ここでは多少の回り道をいとわず、根幹のWhyをしっかりと抑える事を

意識してご説明しています。

そうは言いつつもですね、日々の多忙にかまけてほぼ1年、放置して

しまっている事に気付き、猛省しております…。

来週には少しずつでも更新しようと思います。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2014/11/04(Tue) 12:25 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

うわぁこちらは半年経過…。ネタを抱えて更新しないのは言い訳のしようがありません。こちらも近日更新いたします!

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/02/28(Sat) 21:53 |

| 投稿者 |

: ブラッドヴォルス |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

更新期待してます。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/03/09(Mon) 00:40 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ブラッドヴォルスさん、ありがとうございます!

こんどこそ本当に(大汗)、近日更新いたします。

編集

【旧BBSから移行】ロードスイッチでトラブル発生!そこでの応急処置のお話(1)

| 投稿日 |

: 2015/03/17(Tue) 23:40 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

はい、しばらくぶりの更新になります。

古いネタからご紹介していこうと思います。

ここの記事つながりですので、ロードスイッチですね。

PチャネルMOSFETを使用して、ハイサイドスイッチを構成した

製品でのトラブル発生と応急処置の事例をご紹介します。

制御回路の電源と、負荷の電源は共通の5Vで、

リチウム系2次電池の12V系からレギュレータで降圧したものでした。

編集

【旧BBSから移行】ロードスイッチでトラブル発生!そこでの応急処置のお話(2)

| 投稿日 |

: 2015/03/17(Tue) 23:43 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

以前の図を再び掲載しますが、この構成ですね。

編集

【旧BBSから移行】ロードスイッチでトラブル発生!そこでの応急処置のお話(3)

| 投稿日 |

: 2015/03/18(Wed) 00:06 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

制御回路にはマイコンを使用していました。

マイコンのプログラムに従って、負荷をオン・オフするわけですね。

ところが、負荷をオンした途端、マイコンがリセットされてしまったのです。

動作の途中で突然リセットされちゃあ、狙い通りの機能なんて実現できっこありません。

トラブルの発生です。ここから原因調査と応急処置が始まります。

続きはまた近日。最近、睡眠が不足すると翌日は使い物にならなくなりました。

皆様も夜更かしにはどうぞご注意ください。

それでは、おやすみなさい。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/03/25(Wed) 00:03 |

| 投稿者 |

: tkn |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

大型7セグのコモン制御に悩んでいて、画像検索からたどり着きました。

具体例が多くて助かります。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/03/25(Wed) 19:52 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

tknさん、はじめまして。

ご覧いただきありがとうございます。

そうですね、7セグなどのLEDのダイナミック点灯制御には、

コモン(共通線)の制御に比較的大きい電流のスイッチングが必要ですよね。

アノードコモン構成の場合、

PチャネルMOSFETを使用したハイサイドスイッチになると思います。

カソードコモンの場合はNチャネルMOSFETでローサイドスイッチですね。

MOSFETを使用される場合は、下記の点にご留意をいただければと思います。

マイコンの出力ポートを直接MOSFETのゲートに接続される場合、

その電圧で充分にオン状態となるMOSFETは限られてきます。

データシートでゲートスレッショルド電圧(Vthなどと記載されます)や、

ゲート電圧ごとのオン抵抗(Ronなどと記載されます)を参考に、吟味してみてください。

同じく出力ポート→ゲート直結の場合、オン/オフに比較的長い時間がかかる事が多いです。

ある桁をオフしてすぐに次の桁をオンすると、表示に乱れが現れるかもしれません。

その場合は桁切り替えの間に少し待ち時間…どの桁も点灯させない期間…を入れてみてください。

ソフトウェア制御の場合、1命令サイクルで充分だと思います。

アセンブラだとNOP命令とか、C言語などでもNOP()擬似関数やマクロが用意されていると思います。

その間に個別線の状態を変更すればいいわけですね。個別線というのは、各セグメントにつながる配線です。

流れとしては、以下のようになります。

ある桁をオフ→NOP→個別線の状態を変更→NOP→次の桁をオン

上手くいきましたら、ぜひここで自慢話をお願いします。

今ひとつ盛り上がりに欠けているのが、ここでの悩みなんです。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/11(Sat) 13:24 |

| 投稿者 |

: N.K |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

始めまして、ロードSWを調べていて辿り着きました。

判りやすい解説で助かります。

便乗で申し訳ないのですが、ご質問があります。

低電圧(6V)、大電力(60A)をON/OFFするN-chFET使用のハイサイドロードSWを作ろうとしています。

PWMは無しでスイッチのON/OFFの頻度は数分に1回ぐらいです。

出来るだけ低オン抵抗にしたいのでN-chを使用したいと考えています。

単純にN-chFETのゲートにDC-DCで昇圧した15VぐらいTLP250あたりで入れようと考えて色々調べて気になる事が出てきました。

似たような回路をしらべると大体DC-DCは絶縁型を使用する旨が書かれています。

コントロールする側の電圧(6V)よりも高いので非絶縁でも良いのではと思ってし

まうのですが絶縁で無いと駄目な理由があるのでしょうか?

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/12(Sun) 00:14 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

みなさま、おひさしぶりです。

また近日更新すると申しておきながら、またひと月近く経過してしまっていたり。

なんだか、やるやる詐欺の様相を呈してきております。

このところ、私の前に立ちはだかっていたいくつかのハードルを乗り越えたところです。

最も高く、乗り越え難かったハードルは、自らの先入観や固定観念でした。

ひとりで悶々と考え続けていても、なかなか出口を見出せないものです。

N.Kさんはじめまして。ようこそいらっしゃいませ。

便乗も大変結構でございます。ぜひぜひ話題をお寄せください。

60Aですか…でかいですね。

ご質問の趣旨から脱線してしまいますし、ご存知でしたらすみません。

転流(フリーホイール)ダイオードやツェナー、スナバなどの各種対策を

充分に検討された上に、なるべくゆっくりとオン/オフされると良いと思います。

直流の大電流をオン/オフする必要のある状況では、寄生インダクタンスが最大の敵です。

インダクタンスが大きいほど、またそこに流れる電流が大きく変化するほど、

またその変化が短い時間で行われるほど、大きな逆起電力が発生します。

充分な対策が施されていない回路の誤動作や破壊をもたらします。

インダクタンスが主要因ですので、負荷までの配線も極力太く短くが鉄則です。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/12(Sun) 01:10 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

さて本題に戻りましょう。

絶縁電源が必要だと思います。

Nチャネルでハイサイドスイッチを構成すると、

ソース電位が変動するので、

ゲート電位の与え方が難しいんですね。

図をご覧ください。

MOSFETが確実にオン/オフできている仮定で、

スイッチと見なしての図です。

電源電圧はご質問と同じ状況で6Vです。

スイッチがオフの状態では、ソース電位は

負荷を通じて弱い(ほとんど電流を流せない)0Vです。

スイッチがオンの状態では、ソース電位は6Vです。

NチャネルMOSFETのほとんどの品種を確実にオンさせる

には、ソース電位を基準としてゲート電位を10V以上高く

してあげる必要があります。

ソース電位が基準と書きました。そしてこの基準が

変動してしまう事もご説明しました。

変動する基準に対して一定の電位を作り出すには、

絶縁電源が容易で確実な方法かと思うのです。

絶縁って表現だと、いらないよねって印象がありますが、

フローティングって表現が今回ピッタリくるでしょうか。

出力電位が、入力電位と何の関係を持っていないので、

都合が良いのです。

私は実績を持っていないのですが、ゲート電位を用意する

だけでしたら、「フォトボル」はいかがでしょう?

LEDと光電池を組み合わせた部品で、出力電流はほとんど

取れないものの、それだけで絶縁電源として機能します。

光起電力(電圧)が不足するようなら直列接続します。

電池ですからね。

フォトボルは東芝の商標のようなのですが、他社からも

光起電性フォトカプラとか、MOSFETドライバとかの名称で

出ています。

速度が遅いのが短所のようですが、

ご質問の件では高速動作は不要のようですし、逆起電力を

考慮するとむしろゆっくりオン/オフしたいわけですから

問題にはならないのかなと思います。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/13(Mon) 19:57 |

| 投稿者 |

: N.K |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

詳しい解説ありがとうございます。

フリーホイールダイオードはどの程度の物が必要か

悩み中です。

後、ゲート電位に関して更に御聞きしたい事があり

ます。

例えばVGSS=20VのN-chFETで先の回路を考えた場合

、6Vから非絶縁型のDCDCで16Vを作りゲートに与える

とするとソースが0Vの時は電位差16Vが与えられソー

スが6Vの時は電位差が10Vになると思います。

これだと問題有るのでしょうか?

因みに非絶縁型の方が探した限りサイズがよさそう

な物が多い為非絶縁型で行けたらと思っていまし

て。

フォトボルは存じ上げていませんでした。

ただ調べた範囲では今回使用予定のFETとの組み合わ

せでよさそうな物が見当たらなかったのとFETをパラ

で使用しようと思っている関係で使えなさそうで

す。

ただ使える条件の時はとても手軽そうなので今度試

してみます。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/20(Mon) 00:27 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

すみません、1週間のご無沙汰でした。

フリーホイールダイオードの選定は、意識してスイッチング速度を遅くできれば

あまり難しく考える必要はないと思います。

負荷電流が最大60Aとの事でしたので、60A流せるダイオードであればOkでしょう。

意識してスイッチング速度を遅くするには、ゲート電位の変化を遅くするのが

安易な方法だと思います。RC積分回路が単純かつ確実ですね。

どの程度遅くすれば良いかの目安はケースバイケースになってしまうと思います。

負荷とそこまでの配線にどれほどのインダクタンスが存在するかで変わってきます。

ゲート電位の変化速度と、スイッチング速度はイコールではなく、

ゲート電位がしきい値電圧VTH付近を横切る速度ですので、実験で最適値を探る

必要もあります。あらゆる時点においても電圧・電流が安全動作領域内に収まって

いる必要もあります。電圧・電流それぞれが定格に近い場合は特に要注意です。

ご提示いただきました方法、なるほど行けるかもと思いました。

負荷の種類によっては、オフ時にソース電位があやしくなる(しっかりとした0Vに

ならない)可能性も考えられますので、事前に充分な評価検討は必要かと思います。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/24(Fri) 09:32 |

| 投稿者 |

: T.F |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

はじめまして。こちらの記載のあることで悩んでおりましたので、参考にさせていただいております。まさに自分の考えていた回路構成やその際の抵抗選定などが記載されており、本当にありがたいです。

さて、[125]ロードスイッチでトラブル発生!そこでの応急処置のお話(3)の続きが気になり記載させていただきました。

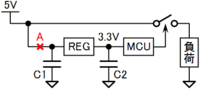

現在考えている構成は[35]の回路のもので、3.3V動作のMCUを利用して5V3~5A程度の負荷をスイッチングすることを考えています。

MCUへの電源は同じ5VからDC変換したものを利用する形です。

DC変換の回路や性能にもよるかと思いますが、想像するにブラウンアウトしてしまっているということで良いでしょうか?

その場合は負荷側へ直列でインダクタを入れればよいかと思っていますが、如何でしょうか?

インダクタの選定方法などお聞かせいただけると助かります。

よろしくお願いいたします。

では

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/24(Fri) 12:23 |

| 投稿者 |

: N.K |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

詳しい解説ありがとうございます。

フリーホイールダイオードは60Aで済めば嬉しいところです。

(結構大きくなってしまうので。)

速度はオシロで見ながら実験していきたいと思います。

後、ゲートの件もありがとうございます。

しっかり0Vは注意して実験してみます。

ありがとうございました。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/27(Mon) 23:24 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

N.Kさん、はたしてお役に立てたかどうか、自身が無いのですが、

目的を達成される事をお祈りしております。

大電流ですのでステップバイステップで段階を踏んで、

安全第一で実験を進めてみてください。

首尾良く上手く行っても、あいにく上手く行かなくても、

はたまた全く異なるネタでも、ぜひともまた話題をお寄せください。

お待ちいたしております。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/28(Tue) 01:25 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

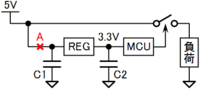

T.Fさんはじめまして。ようこそいらっしゃいませ♪

お話の続きね、ぜんぜんできてないんですよね。

風呂敷広げっぱなしで申し訳ないです。

実は、N.Kさんにご提供いただいた話題で、

結果のタネ明かしをしてしまってはいるのですが、

近々、時間を作ってきちんとまとめを書きます。

ひょっとすると、すでにお困りの状況に直面されて

いるのでしょうか。だとすると私、責任重大ですね。

私の場合は、電源電圧がごく短時間だけ低下して、

ブラウンアウトを回避するためのリセット回路

(BOR:ブラウンアウトリセット)が動作してしまって

いました。停止(ブラウンアウト)よりマシとはいえ、

それまでの動作が中断されて再起動(リセット)という

のは問題でした。

電源電圧低下の原因は、突入電流でした。詳しくは

元記事のまとめできちんと書きますね。スイッチを

「ドン!」と入れるから電流も「ドン!」と流れる

わけで、スイッチを「ジワッ」と入れると電流も

「ジワッ」と流れてくれるので、これで解決しました。

T.Fさんにご説明いただいた回路構成は、図のような

感じでしょうか?インダクタも解決策のひとつとして

アリなのですが、コストと占有スペースが大きいのと、

逆起電力とそれに起因するアークなど、副作用も大きい

ので、もっとお手軽な対策から試される事をお勧めします。

図の回路構成でしたら、最近私が好んで採用する方法では、

・A点にダイオードを挿入する

・C1の容量を増加する

です。ダイオードは大元の5Vが低下してもA点の右側は

低下させません。その間、A点右側の電圧は容量アップした

C1が維持するわけです。

ただあくまで、最近の私のマイブームですので、

回路設計者の多くが採用する万能定番の方法ではありません

のでご注意ください。定番の回路というものは、なかなか

無いものです。回路設計も奥深い世界ですね…私もまだまだ

道半ばです。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/28(Tue) 14:34 |

| 投稿者 |

: T.F |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

お答えいただきありがとうございます。

自分の考えておりました回路は、まさに記載いただいたものです。

私も説明が悪かったのですが、ご指摘の通りBORが発生するというものでした。

使用しているレギュレータはダイオードによる降圧で4.3V程度であっても問題無く3.3Vが出力されるようでしたので、こちらの解決方法で使用してみたいと思います。

基本的なことの質問になってしまいますが、使用するダイオードは一般整流用のダイオードでよろしいでしょうか?

C1の容量など実際のパーツ選定は、レギュレータやMCU周りの消費電力、突入電流や大元の5V出力を行う電源の性能などのよるかと思いますが、一般的なお話をお伺いできると助かります。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/04/30(Thu) 23:38 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

ダイオードはショットキーバリア型がいいでしょうねえ。

どうしても、ダイオードの通過後で電圧降下が生じてしまいますので。

大き目の電圧降下も許容できて、使用電流も小さ目であれば、この検討項目の優先度は低くなります。

いずれも品種や周囲温度、電流により様々なのですが、一般整流用ですと0.6〜0.8Vの電圧降下が生じます。

これがショットキーバリア型ですと0.3〜0.7Vと結構改善されます。

これらの電圧降下は、各ダイオードのデータシートで確認できます。

「順方向電圧降下」や、「Forward Voltage Drop」と記載されます。

記号は「Vf」です。数表に記載の値は、参考程度にしてください。

比較には使用できません。なぜなら測定条件がバラバラだからです。

なるべくグラフで、使用する周囲温度・電流で値を見るようにします。

電流定格は、その先の負荷回路(主にマイコンですかね)に合わせます。

せいぜい数十〜数百mAでしょうから、小信号用でも足りると思います。

サージ電流(非繰り返しピーク電流などと表現される場合もあります)には余裕があったほうが良いでしょう。

電源投入時、コンデンサC1にはそれなりに大きな突入充電電流が流れますので。

コンデンサC1は、ドンブリで良ければ100〜1000μFの電解コンデンサで充分でしょう。

汎用品が良いです。低ESR品とか、OSコンなどの固体高分子コンデンサなどは考えないほうが良いです。

また突入電流に悩まされてしまいます。電解コンデンサはESRもESLも大きいのですが、突入電流を抑えるには

それが都合が良いのです。

厳密に設計するのならば、Q=CV, Q=Itの2つの式で算出します。

簡単な例として、通常は4Vが供給されていて、これが断たれた時に3Vまで降下しても良い場合に100μFを採用すると、

4V供給時に充電されている電荷は、

Q=CV=100[μF]×4[V]=400[μC]

3Vまで降下した場合の残留電荷は、

Q=CV=100[μF]×3[V]=300[μC]

これらの差、放電により失われる電荷は、

400[μC]-300[μC]=100[μC]

その先に流れる電流が簡易的に10mA一定としましょう。10mAの電流を、100μCの電荷でまかなえる時間は、

Q=It=100[μC]=10[mA]×t

t=10[ms]

10ミリ秒の間、大元の電源が断たれても、マイコンは動作を続けられるわけです。

この間に大元の電源が回復すれば良し、それ以上の期間断たれるようならより大きい容量を選択する、

のような手順になります。逆の手順なら必要な容量が答えとして得られますね。

これらの数式は私も最近使うようになりました。ですので説明がイマイチかもしれません。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/05/02(Sat) 07:01 |

| 投稿者 |

: T.F |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

詳細にお答えいただきありがとうございます。

なるほど、そのようにコンデンサを決定しているのですね。

いつもドンブリと周りの回路の例から100~470uF程度にしていました。

参考にして作成してみます。

ありがとうございます。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2015/06/25(Thu) 14:50 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

しばら〜く更新できてません。ガリガリと仕事ばかりしています。

まあ、雑談部屋ですので、まったりとして行きたいと思います。

お許しをいただけましたらと思います。

最近の私の仕事では、小さな電池で長期間の動作を求められるケースがしばしばあります。

多くの場合の解決策として、間欠動作が第一の候補に挙がります。動作に必要な期間を除いては、消費電流をゼロに近づけるのです。このため、休眠中に不要となる回路は、電源を切ってしまいます。そこで出番となるのが、オン・オフを自在にコントロールできるロードスイッチなんですね。

いま考えているのが、マイコンの出力ポートをロードスイッチとして使用する事、つまり出力ポートの先に負荷をつないでしまう方法です。

マイコンの出力ポートは、現在では多くの場合、MOSFETによるスイッチが2つで構成されています。

1つ目のスイッチは、プラス電源(VddとかVccとか呼ばれます)から出力に接続されています。これがオンになると、出力はプラス電源とほぼ同じ電圧、つまりハイレベルになります。

2つ目のスイッチは、マイナス電源(VssとかGNDとか呼ばれます)から出力に接続されています。これがオンになると、出力はマイナス電源とほぼ同じ電圧、つまりローレベルになります。

同じ端子を、入力ポートに設定できるマイコンも多いですね。

この場合、自らハイ/ローレベルにする事はありませんので、1つ目のスイッチも、2つ目のスイッチも、共にオフにします。

詳しくはまた別の機会に触れる事にしますが、共にオンになる状況も…瞬間的には起こり得ます。プラス電源とマイナス電源が接続されるわけで、これはショートとか短絡と呼ばれる状況なのですが、瞬間的とはいえ大きな電流が流れてしまうわけで、非常にまずいのです。この現象は貫通電流とも呼ばれます。気になった方はググってみてください。

閑話休題、ロードスイッチとしては1つ目のスイッチをハイサイドスイッチとして使用する事を考えています。これをオン、つまりポートを出力モードにしてハイレベルを出力してあげれば、これを電源電圧として負荷が動作してくれます。

これをオフ、つまりポートを入力モードにしてあげれば、負荷の電源はどこにもつながらなくなりますので動作しなくなります。

ただマイコンの出力ポートは、取り出せる電流が小さく(負荷の消費電流も小さいのでこれは問題にならない)、これはスイッチとしての性能が良くない…オン抵抗が大きい事を意味しており(負荷への供給電源電圧が降下してしまうのでこれは問題)、対策として複数のポートを接続して同時に操作する方法を考えています。状態を一度に切り替えられる複数ポートであればこの技が有効だと考えています。

さてさて、どうなることやら。結果が出たらまた報告します。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2016/01/19(Tue) 13:10 |

| 投稿者 |

: N.K |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

N.K

お久しぶりです以前お世話になりましたNKです。

以前ご相談した件は結局絶縁型DC-DCを使用しました。

非絶縁型を使用した所ご指摘の様に停止時にソースが0Vに成らない事が有りNGでした。

それで又お聞きしたいのですが、ハイサイドN-CHのロードスイッチやHブリッジの回路を調べているとVGS用電源ににブーストラップを使用した例が、良く出てきます。

この場合ブーストラップは非絶縁電源に成ると思うのですが何故問題ないのでしょうか?

基本的な質問の様な気もするのですがご教授頂ければ幸いです。

編集

【旧BBSから移行】N.Kさんおひさしぶりでございます!

| 投稿日 |

: 2016/01/20(Wed) 22:50 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

N.Kさん、ご再訪ありがとうございます!嬉しいです。

さて、なぜ絶縁電源が重宝されるかと申しますと、出力側の基準電位が自由に決められるからなんです。

そもそもMOSFETはゲート・ソース間電圧VGSによってオン/オフ動作を行います。

ソース電位VSを基準にしたゲート電位VGが、ゲート・ソース間電圧VGSです。

NチャネルMOSFETでハイサイドスイッチを構成すると、そのオン/オフでソース電位VSが変動します(まあこれは、電源入力のマイナス側をGNDとかVssとかと呼んで、これを全ての基準にして考えるからなのですが)。

変動するソース電位VSに対しては、同じように変動するゲート電位VGを与えてやらないと、一定のゲート・ソース間電圧VGSを与えた事にはならないですからね。

このへんの問題がクリアさえできれば、絶縁でも非絶縁でも構わないんです。

さらに始末が悪い事に、オフ時のソース電位VSは不定です。

負荷と並列に抵抗を接続して、オフ時のソース電位VSをGND電位に引き下げる手もアリだとは思いますが。

ゲート・ソース間と並列に接続する抵抗(これまでの図ですとR1)はあらゆる場合で不可欠です。

このへんの対策をキチンとするとソース電位VSは、GND電位と電源入力のプラス側電位(N.Kさんのケースでは+6Vでしたっけ?)の間となります。

こうなると非絶縁電源でも、15Vくらいのものをご用意いただければしっかりオン/オフ動作させられるとは思います。

15Vくらいの根拠は、入力電源電圧プラス、MOSFETを充分にオンさせられるゲート・ソース間電圧VGSです。

これはMOSFETの品種により異なりますが、昔からあるものでは大体10Vくらいが必要です。最近はもっと低い電圧でしっかりオンしてくれるものも出ています。

でもね、MOSFET1個のゲート駆動のために、わざわざ絶縁ないし非絶縁の電源を別に用意するというのは、やはりもったいない感覚があります。

以前にもご提案させていただいたのですが、オン/オフの頻度が低いとの事でしたので、フォトボルが向いていると思うのですがいかがでしょうか?

これも一種の絶縁電源だと思います。

http://toshiba.semicon-storage.com/jp/product/opto/photocoupler/photovoltaic-output.html

フォトボルは電流供給能力が低く、ゲート寄生容量の充放電に時間が掛かりそうです。この結果オン/オフもゆっくりしたものになり得ます。

ただ、以前にうかがったところでは電流がかなり大きいので、dI/dtを低く抑えられるメリットにもなりそうです。

さて、ご質問のブーストラップは一種のチャージポンプですので、オン/オフが繰り返される用途でないと適用できません。

スイッチング電源回路やD級アンプ(これも一種のスイッチング電源です)などでの用途に向いていますね。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2016/01/24(Sun) 22:46 |

| 投稿者 |

: N.K |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

お世話になりますN.Kです。

詳しいご説明ありがとうございます。

ブーストラップは何故絶縁で無くとも良いのかで悩んだのですが、VSに連動さえすればよいのですね。

(仰る通りブーストラップはデュティー100%に出来ないのでこの場合使えなかったのですが。)

フォトボルは検討したのですが入手性が悪いのと使用するFETに有った電圧で都合の良い物が無かったの

で見合わせました。

どうもありがとうございました。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2016/01/25(Mon) 23:51 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

はい。絶縁型とはいえ、どこかに接続すると非絶縁ですからね。

ただ基準電位をどこにでも自由に持っていけるというメリットがあります。

逆に、GNDを基準電位としてつじつまが合わせられるのであれば、出番が無いとも言えます。

入手性は肝ですよね。入手できない部品は存在しないに等しいですから。

メーカーや流通の関係ご各位には一層の努力をお願いしたいところです。

N.Kさん、ぜひまたお立ち寄りくださいねー!

編集

【旧BBSから移行】PWM駆動とMOSFET, ゲート抵抗の選定について

| 投稿日 |

: 2016/05/13(Fri) 03:59 |

| 投稿者 |

: いろはす |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

お世話になります。

MOSFETのスイッチングを調べていたところ、こちらにたどりつくことができました。

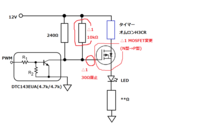

MOSFETとバイポーラTrもしくはデジトラを組み合わせ、タイマーON,OFFとLEDを点滅(Lチカ)させて理解を深められる工作をしたいと考えております。

(本日時点ではタイマーの場所をショートさせております)

そこで、ご相談があります。

現在動作確認をしており、PWM-デジトラ単体のON/OFF切り替え動作は問題ありません。

しかし、後段のMOSFETに接続して動作検証したところ、MOSFETが仕事をしてくれない事態が発生しました。怪しいところは目星をつけているのですが、確証が持てていない状況でございます。

どの箇所に原因があるかご教示いただけないでしょうか?

「ここをこう直すと良くなる」といったご提案もいただけると幸いです。

当方の都合で恐縮ですが、ハイサイドスイッチ構成でソース側に負荷を接続したいと考えています。

自分で怪しいと感じているのは次の2点です。

一つ目は赤枠の30Ωのゲート抵抗です。

この箇所の抵抗が低いためにオンに至らなかった?と推定しています。

ゲート抵抗をつけている回路図もあれば、そうではない回路もあります。基準は何でしょうか?

抵抗値も10k近く入れていたり、10Ω程度しか入れていなかったり…とまちまちです。

もう一つは、PWM駆動しているデジトラです。

デジトラの利得が低く力不足のため、MOSFETを

OFF状態にできないのではと考えております。

ご多用のところ誠に恐縮ではございますが、以上宜しくお願い致します。

編集

【旧BBSから移行】しまったあー!!

| 投稿日 |

: 2016/05/16(Mon) 15:13 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

いろはすさん3日も放置してしまい申し訳ありません!

今日か明日にはきちんとしたご説明をつけて回答いたします。

もうしばしお待ちくださいませ。

編集

【旧BBSから移行】RE: PWM駆動とMOSFET, ゲート抵抗の選定について

| 投稿日 |

: 2016/05/18(Wed) 02:39 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

いろはすさん、お待たせいたしました。

色々と工夫をされているようですね。

結論から申しますね。

この回路構成ですと、MOSFETはオンとオフの中間状態になってしまうと思います。

要点がいくつかあります。

絶縁電源、ブートストラップ、フォトボルなどのフローティング電源が用意できない回路では、ソース電位が変動してしまうような回路構成、具体的にはソース側への負荷接続は避けるべきです。

ほぼ例外無く、ゲートとソースは数10k〜数MΩの抵抗で接続するべきです。

ゲート抵抗は、スイッチング速度が速過ぎて問題になる場合(誘導負荷とdI/dtから生じるノイズ発生など)に挿入します。そうでない場合は不要ですが、挿入されていたとしても影響はありません。なおゲート抵抗はゲート寄生容量と1次遅れ回路を構成するものですので、値が大きいと遅れは大きく(スイッチング速度は遅く)、値が小さいと値が大きいと遅れは小さく(スイッチング速度は速く)なります。MOSFETの品種によりゲート寄生容量は異なりますので、ゲート抵抗の最適値もまた異なってきます。

結局何をどうすれば良いのか?と申しますと、もしハイサイドスイッチをご所望でしたら、NチャネルではなくPチャネルのMOSFETを使用されるのが良いかと思います。

編集

【旧BBSから移行】RE: PWM駆動とMOSFET, ゲート抵抗の選定について

| 投稿日 |

: 2016/05/22(Sun) 20:58 |

| 投稿者 |

: いろはす |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

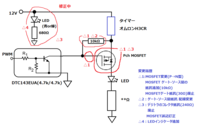

中の人1号さま

アドバイスをいただき有難うございます。

こちらこそご連絡がおくれてしまい、大変申し訳ありませんでした。

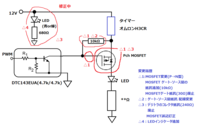

Pch型ハイサイドスイッチの駆動回路に設変しました。

内容:

G-S間に抵抗10kΩを入れ、入力不定状態を回避。

スイッチング速度は気にしないものなので

30Ω廃止。

負荷(添付図ではLEDと抵抗になっています)を下流につけ、動作検証をしていきたいと思います。

基本動作は、デジトラがON/OFFすることでPchのMOSFETもON/OFFを繰り返します。

で、タイマーが切れたときはMOSFETがON状態でもLEDは点灯しません。

シンプルですが、スイッチング動作とタイマーの機能を視覚的に理解できるようになると考えております。

ご多忙にもかかわらず、わかりやすいご説明をいただき誠に有難うございました。

今後とも宜しくお願い致します。

編集

【旧BBSから移行】RE: PWM駆動とMOSFET, ゲート抵抗の選定について

| 投稿日 |

: 2016/05/22(Sun) 23:22 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

いろはすさん、まだご覧になられてますでしょうか?

もうワンチャン、フォローさせてくださいね。

Pチャネルに変更されますので、ソースが+側、ドレインが-側に変わります。

書いていただいた回路図ですと、上下反転されると正しい接続になります。

G-S間の抵抗10kΩですが、上側の接続点は+12Vよりタイマーの下側をおすすめします。

タイマーがオフになるとG-S間じゃなくなっちゃいますからね。

もうひとつ、ご変更された回路では240Ωは不要になりますね。

デジトラの負担をいたずらに大きくしてしまいますので。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2016/05/23(Mon) 23:39 |

| 投稿者 |

: いろはす |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

中の人1号さま

重ね重ねアドバイスをいただき、有難うございます。

他の予定が立て込んでいて、まだ工作には着手できておりませんのでご安心ください。

中の人1号さまよりいただいたアドバイスを元に、回路図を訂正しました。

(ご指摘の通り、10kΩ直結ではゲート・ソース間抵抗の仕事をしてくれませんね。タイマーOFF時はゲート抵抗に化けてしまっています)

変更点が見えるように○で囲っております。

おまけとして、電源が入ったことが分かるようにLEDインジケータを追加しました。

ご多忙にもかかわらず、お力添えをいただき誠に有難うございました。

今後ともご指導ご鞭撻のほど宜しくお願い致します。

編集

【旧BBSから移行】大変!大変!

| 投稿日 |

: 2016/05/24(Tue) 01:56 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

あーいろはすさん大変です、

△3の箇所の配線は切断しておいてくださいね。

このままですとPWMがHighになってデジトラがオンした途端にパーン!ってなっちゃいますからね。

お仕事、お忙しいんですね。おつかれさまです。

じっくりと回路に取り組めるお時間ができます事、お祈りしてます。

また事後談などお寄せくださいね。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2016/05/24(Tue) 08:56 |

| 投稿者 |

: いろはす |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

中の人1号さま

大変失礼しました(汗)

コレクタに負荷が入ってないですね。

この回路で動かすなら小さい抵抗でも入れて

おかないとオシャカに…

直し中ですが、記事No.166の回路図修正版を

アップしました。

現物は時間を見て、作ってまいります。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2016/05/24(Tue) 11:09 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

> 直し中ですが、記事No.166の回路図修正版をアップしました。

この回路でいいと思いますよ。

コレクタ負荷は必要無い場合は無くても構いません。

コレクタがオープン=どこにも電流の流出入が無い状態ですね。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2016/05/29(Sun) 18:47 |

| 投稿者 |

: いろはす |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

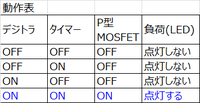

中の人1号さま

度重なるアドバイスおよびお力添えをいただき、有難うございます。

26日より手作り試作品の着手をしました(汗)

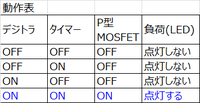

備忘録として検討回路の動作表をアップします。

回路変更でR3を廃止しましたが、実はいてもいなくてもLEDの点灯動作は同じということが、動作表を書いて理解できました

(厳密には、R3が挿入されるとMOSFET立ち上がりが遅くなりますが)。

仮にR3が実装され、デジトラOFF, タイマーONの条件でどうなるか?を検討していましたが(R3と10kΩの閉回路ができるのでちょっと考えてました)、結局、電位差がゲート・ソース間に発生しないためMOSFETはOFFのまま…という理解を得ることができました。

デジトラONでGNDに引っ張ってくれないと、P-MOSFETもONしてくれないですからね。

お忙しい中にもかかわらず、ご助言をいただきましたこと深くお礼申し上げます。

完成しましたら、またご報告いたします。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2018/06/23(Sat) 16:43 |

| 投稿者 |

: nakatan |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

初めまして、時々参考にさせてもらっています。

お知恵を拝借したく投稿いたします。

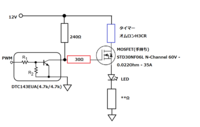

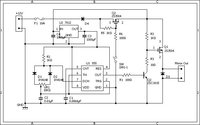

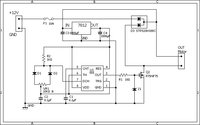

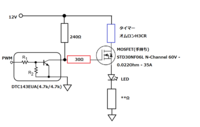

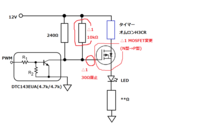

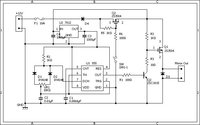

カーエアコンのブロワーファンをPWM制御したく既成のPWMコントローラーを購入しました。

机上での試験はOKでしたが購入したPWMコントローラーはローサイドドライブで取り付ける車のブロワーモーターが(-)コモンの為、ハイサイドドライブにする必要が有ります。

そこで終段のFETをN-ChからP-Chに交換しました。

結果一応動くには動きますがフルパワーが出ないのとFETが発熱します。

ゲートの抵抗を変えたりバッファーを設けたり色々試行錯誤をしましたが巧く行きません。

交換したFETの選定の問題か回路の不備なのか?回路図を添付しますのでアドバイス戴ければ幸いです。

因みに改造前に電流を計ったら最大風量時13A程流れていました。

宜しくお願いします。

編集

【旧BBSから移行】nakatanさん、いらっしゃいませ〜

| 投稿日 |

: 2018/06/24(Sun) 19:34 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

nakatanさん、はじめまして。ようこそいらっしゃいませ。

回路図を拝見しました。

これ、Nチャネルのローサイドから、Pチャネルのハイサイドに、単純にFETを替えただけではなさそうですね?前段、2SC1815の部分も、Pチャネル向けに上手く組まれてるように見えます。

これといって問題のなさそうな回路なのですが、上手くいっていないとすれば、ソースとドレインが逆になっているのではないでしょうか。

回路図上の、おそらくはメインスイッチの働きをする2SJ504も、回路図右の、PWMスイッチを行う2SJ504も、図記号の通りですとソースとドレインが逆のようです。

それぞれ、R5とR3がソース・ドレイン間に入る接続が正解になります。

もうひとつ気になったのですが、ブロワーファンで12V・13Aというのは大きすぎるように思えます。相当強力なファンでも、12V・数Aといったところなのかな、と思います。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2018/06/25(Mon) 14:51 |

| 投稿者 |

: nakatan |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

中の人1号様

早速の回答ありがとうございます。

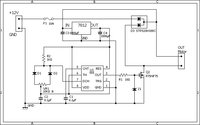

ご指摘の様に回路図のFETの向きが逆でした、手元の図面は修正しました。

Pin番号は正しく実際の回路も接続は合っております。

小生真空管世代でFETを使用するの初めてでして。(^-^;

それとご指摘の様に当初は555で直接2SJ504をドライブしていましたがゲート電圧の変化が鈍いので555の後に2SC1815を追加しました。

元(既製品)の回路図(パターンを見ながら自分で起こしたものですが)を添付します。

ブロワーモーターの電流は車のエンジンをかけた状態(約14V)で風量Hiの」状態でクランプ電流計で計ったものですが余り正確ではないかもしれません。

宜しくお願いします。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2018/07/06(Fri) 00:34 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

nakatanさんこんばんは。

なかなかすぐのお返事ができておらず心苦しいです。

実際の接続が合っているとなりますと、ますます正しく動作してくれる気がしてしまいます。

R5(1kΩ)がQ2のソース・ゲート間に、R3(1kΩ)がQ1のソース・ゲート間に接続されているのですよね?

Q1のスイッチング動作は、U1(555)の発振周波数になりますので、オシロスコープでもなけれは確認は難しいと思います。

Q2は電源スイッチなのですね?おそらく、SWの電流容量が小さいがために入れられているのかと思います。このスイッチング動作は、SWの開閉によるものですので、テスターでも確認が可能かと思います。

Q2のソース・ゲート間、R5(1kΩ)の両端でも同じですね。ここをテスターの電圧レンジで見て、SWがオフの時は0V、オンの時は11Vほどになるかと思います。だとしますと、Q2はしっかりとオンできると思います。

まず、Q2のスイッチング動作だけを確認される事をおすすめします。Q1のスイッチング動作をキャンセルするには、Q1のソース・ドレイン間を短絡されるのが手っ取り早いでしょうね。

Q2のスイッチング動作だけでファンモーターを回転させてみて、Q2は発熱するでしょうか?Q2がオンの時は、Q2のソース・ドレイン間電圧はほぼ0Vになると思うのですが…。ある程度の電圧が現れるなら、それに電流を掛けた電力がQ2で損失消費されてしまいますので、損失電力分の熱が発生してしまいます…。

どうぞ段階を追って確認されてみてください。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2018/07/10(Tue) 23:17 |

| 投稿者 |

: nakatan |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

中の人1号様、先週から出かけておりまして返事が遅くなりました。m(__)m

本件昨年春頃の事で色々試行錯誤しましたが解決出来ずに棚上げにしておりましたが当時はオシロで波形も観測しました。

幾つかオシロの画像を記録したのですが画像に対して条件などを記載していなかったので定かではないですが出力を上げて行くとQ1のゲートのローレベル電位が高くなってしまう感じでした。

Q2の方はちゃんとスイッチして出力電圧も安定しており素子の温度も上がりません。

少し時間が出来たら再度実験してもう少し整理した上で波形の画像を添えて再度投稿させていただいて宜しいでしょうか?。

余談ですがPWMコントローラは完成品が結構販売されておりますが私が調べた限りどれもローサイドドライブの物ばかりですが何か理由は有るのでしょうか?

もしハイサイドドライブで10A強流せる製品をご存知でしたらご教示戴ければ幸いです。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2018/07/10(Tue) 23:28 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

nakatanさんこんばんは。

そうですねえ。波形を拝見できると前に進めそうな気がします。

プローブとグラウンドリードをあてた箇所もお知らせください。

ローサイドドライブはですね、私見ではありますが、Pチャネルで高性能なMOSFETは選択肢が少なく、流通量も少なく、よって価格が高い。設計者はいずれも逆なNチャネルMOSFETでどうにか設計できて、要求も満足できてしまったので、さらにPチャネルの需要が少なくなる、の循環だったと思います。

NチャネルMOSFETで、となりますと、ソース電位がスイッチ動作に関わらず一定となるローサイドが設計しやすいんですね。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2018/07/11(Wed) 21:49 |

| 投稿者 |

: nakatan |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

中の人1号様、ありがとうございます。

なるほど確かにP-Chの方が品数が少ない様ですが需要が少ない?或いは製造コストの問題でしょうか?

そう言えばPーChとN-Chでブリッジを組んで正転/逆転可能な製品は有りましたのでそれを流用する手もありますね

時間が出来たらトライしてみます。

今後ともよろしくお願いします。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2019/12/28(Sat) 19:05 |

| 投稿者 |

: somi |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

初めまして、スイッチとして使用するMOSFETの選び方を悩んでいた際に、こちらの掲示板を拝見し、大変参考になりました。

ハイサイドP-MOS、ローサイドN-MOSのどちらでもスイッチの役割を果たせる事は理解できていたものの、部品の選定時に「どっちでもいい」という状況が個人的に落ち着かず、何かの根拠を持って部品の選定は行いたいと日頃から考えております。

こちらの掲示板で勉強させて頂いたのち、いくつかの回路を制作する中でたどり着いた、個人的な結論としては、「多くの場合でローサイドN-MOSスイッチに利点が多い」という結論になりました。

その結論に至った前提として、まず制御側回路のマイコン等のGPIO端子の初期状態が、多くの場合、

・0(GND直結と考えて扱える)

・数kΩ〜数十kΩのプルダウン抵抗を介してGNDへ接続

・フロート状態(プルダウン、プルアップ抵抗を外付けする事で任意の初期状態にできる)

のいずれかである事から、出力の初期状態は0Vの場合が多いと思われます。

多くの場合、制御回路(マイコン等)への電源投入から出力が変更可能になるまでの間の時間は、負荷側のスイッチはOFFとなっている事が望ましい事から、出力が0Vの時にOFFとなるスイッチが有利であると考えられます。

次に、制御回路側と負荷側の電源電圧について、多く場合で制御側と負荷側が同じ電圧か、制御側の電圧より負荷側の電圧が高い事がほとんどかと思われます。

その場合、制御側の出力を電圧変換せずにそのままの電圧で使用できるスイッチが有利と考えられます。

最後に、回路やコンピュータを扱う場合に、多くの場合で「1はON、0はOFF」と考えるので、制御側の出力が0の際に、負荷側のスイッチがOFFとなっている事が、ヒューマンエラーの防止の観点で有利と考えられます。

以上の事から、ローサイドN-MOSスイッチには、

・スイッチに使用する部品数が少なくてすむ

・制御回路の初期状態を気にする必要がない

・人間の感覚に近い(ヒューマンエラーの防止)

などの利点が多く、ハイサイドP-MOSスイッチに比べて有利な場合が多いかと思います。

もちろん、上記の内容は「多くの場合」なので、回路の構成や要求条件によってはハイサイドP-MOSスイッチが有利な場合もあるかと思います。それが、P-MOS、N-MOS両方が流通していて、N-MOSの方が安価で種類が多い理由の一つなのではないかと考えております。

当方、電気回路等の専門ではないまったくの素人ですので、的外れな内容を書いてしまっていたら申し訳ありません。長くなりましたが、以上が個人的な考えとなります。

では、失礼いたします。

編集

【旧BBSから移行】RE:nMOSとpMOS-FETの使い分け,選び方について

| 投稿日 |

: 2019/12/29(Sun) 14:58 |

| 投稿者 |

: 中の人1号 |

| 投稿元IPアドレス |

: |

| 投稿元ホスト |

: |

somiさんじゃじめまして。ようこそいらっしゃいませ。

すごくよくまとめていただいてありがとうございます!!

余談になりますが、NチャネルMOSFETは作りやすく、先に実用化・普及してきた経緯もあるようです。

半導体物理は私の理解を超えてしまうのですが、主要キャリアがNチャネルでは電子、Pチャネルでは正孔で、移動度が大きく異なるらしいのです。結果、同じ素子サイズ…チャネル幅で合ってるのかな?では定格が大きく異なってくるみたいです。

さて実はここの掲示板、今年いっぱいで閉鎖になってしまいます。もう数日ですね。

これから先はこちらのアドレスでお願いいたします↓↓↓

https://www.e3office.com/bbs/

これまでここに寄せていただきました内容もこれから慌ててお引越しします(汗

編集